# **Homework 3**

(Due date: October 31st @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

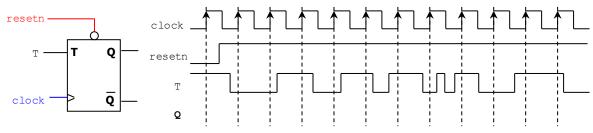

# PROBLEM 1 (12 PTS)

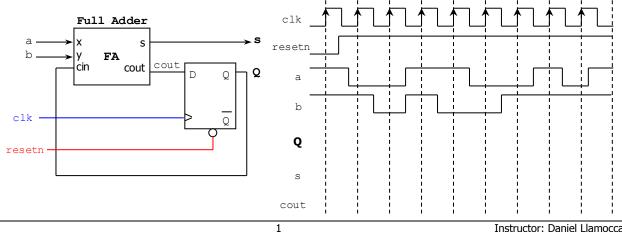

Complete the timing diagram of the circuit shown below. (5 pts) •

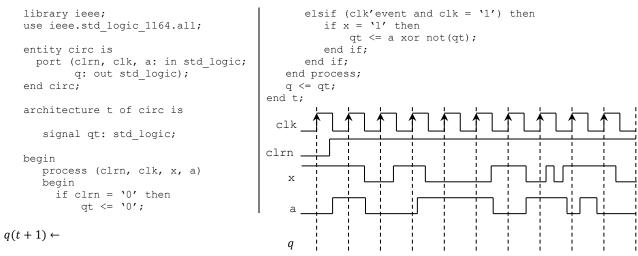

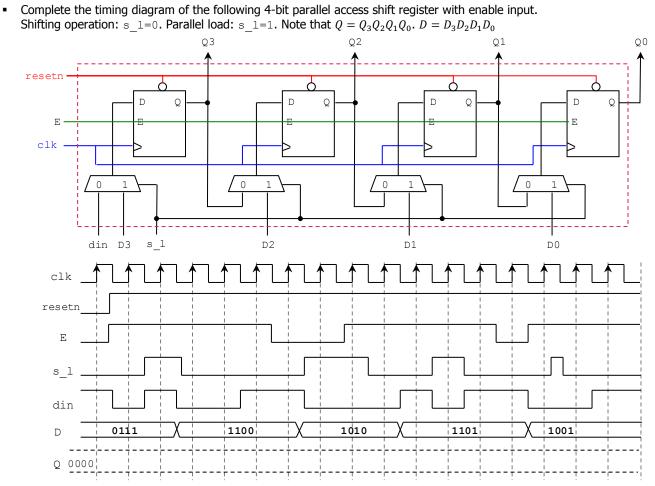

Complete the timing diagram of the circuits shown below: (7 pts) .

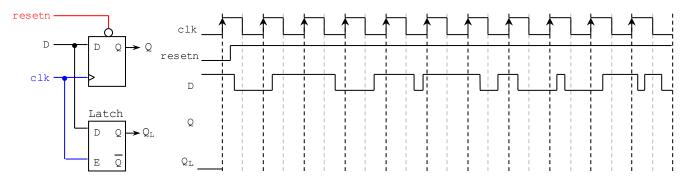

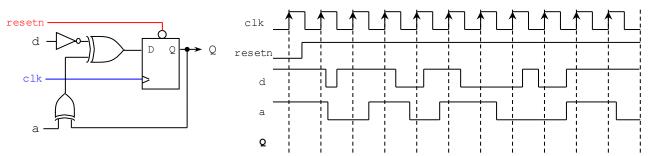

# PROBLEM 2 (17 PTS)

Complete the timing diagram of the circuit shown below: (7 pts) •

Complete the timing diagram of the circuit shown below: (10 pts) .

#### PROBLEM 3 (16 PTS)

- With a D flip flop and logic gates, sketch the circuit whose excitation equation is given by:

- $\checkmark \quad Q(t+1) \leftarrow \bar{x}y + \bar{x}Q(t) + yQ(t) \text{ (4 pts)}$

- Complete the timing diagram of the circuit whose VHDL description is shown below. Also, get the excitation equation for q.

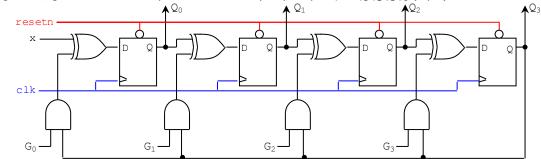

• Given the following circuit, get the excitation equations for each flip flop output  $Q = Q_3 Q_2 Q_1 Q_0$  (6 pts)

#### PROBLEM 4 (18 PTS)

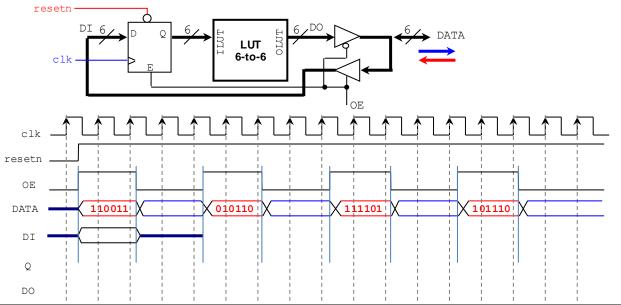

• Given the following circuit, complete the timing diagram (signals *DO*, *Q* and *DATA*). The LUT 6-to-6 implements the following function:  $OLUT = [ILUT^{0.85}]$ , where ILUT is an unsigned number. For example  $ILUT = 35 (100011_2) \rightarrow OLUT = [35^{0.85}] = 21 (010101_2)$

### PROBLEM 5 (12 PTS)

## PROBLEM 6 (25 PTS)

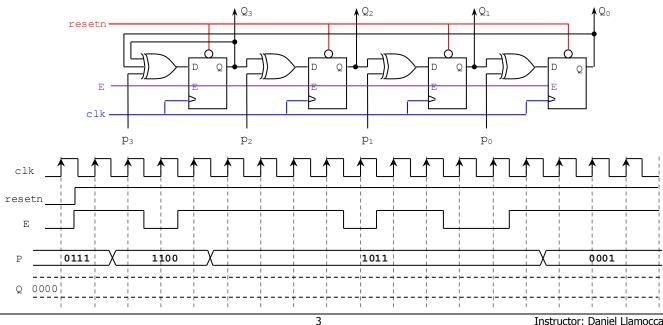

- The following circuit is a multiple-input compressor circuit (MIC), a component in Built-in Self-Test systems.

- $Q = Q_3 Q_2 Q_1 Q_0$ .  $P = P_3 P_2 P_1 P_0$

- ✓ Write structural VHDL code. Create two files: i) flip flop, ii) top file (where you will interconnect the flip flops and the logic gates). Provide a printout. (10 pts)

- ✓ Write a VHDL testbench according to the timing diagram shown below. Complete the timing diagram by simulating your circuit (Behavioral Simulation). The clock frequency must be 100 MHz with 50% duty cycle. Provide a printout. (15 pts)